sleva 20% 1. 5. - 31. 7. 2020

Přes 60 % signálů v na dnešních DPS vyžaduje návrhová pravidla pro high-speed design, EMC nebo bezpečnost. Správnou implementace těchto pravidel je potřeba ověřit po dokončení návrhu, aby se minimalizovala šance na chybu v návrhu. Takové chyby mohou vést k nutnosti opakované reprodukce celého výrobního procesu po předělání části návrhu, což navíc může vést k zavedení dalších chyb.

Přes 60 % signálů v na dnešních DPS vyžaduje návrhová pravidla pro high-speed design, EMC nebo bezpečnost. Správnou implementace těchto pravidel je potřeba ověřit po dokončení návrhu, aby se minimalizovala šance na chybu v návrhu. Takové chyby mohou vést k nutnosti opakované reprodukce celého výrobního procesu po předělání části návrhu, což navíc může vést k zavedení dalších chyb.

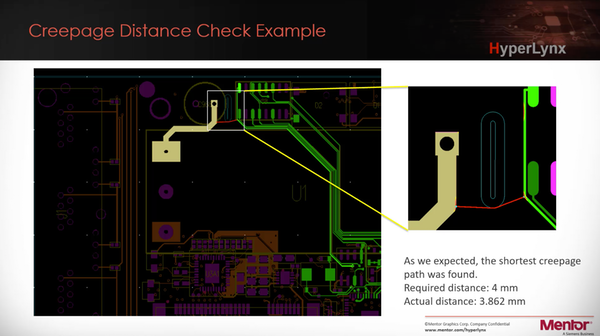

Podrobná simulace každého kroku návrhu každé cesty je časově i odborně náročná, a ne všechna omezení je možné odsimulovat. Problémy s bezpečností jako je elektrický průraz zahrnuje nelineární jevy, které není snadné simulovat.

Výsledkem je, že většina společností věnuje několik málo svých specialistů na SI a PI nejnáročnějších problémů a používá testování prototypů pro vše ostatní. Takový proces je časově náročný a nemusí vést k odhalení všech možných chyb.

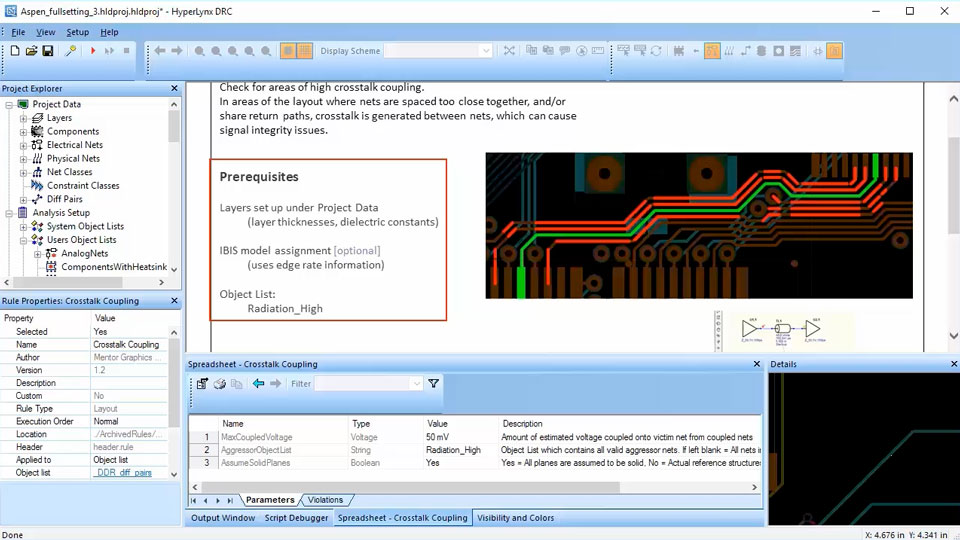

Program HyperLynx DRC je vybaven hybridním přístupem k ověřování v průběhu návrhu. Rychle a automaticky může v jakékoliv fázi návrhu prověřovat DPS na možné nedostatky napříč disciplínami. Potenciální poruchy mohou být zkontrolovány a eliminovány návrhářem díky včasné identifikaci.

Tímto přístupem HyperLynx DRC umožňuje revizi desky prakticky v reálném čase s postupem návrhu. Eliminuje tak zpoždění a problémy s kvalitou způsobené ruční kontrolou prototypu. Současně poskytuje úplné pokrytí vysokorychlostních a bezpečnostních pravidel.