## **PCB Layout**

# **x**pedition<sup>®</sup>

Xpedition is the technology leader for creating today's most complex PCB designs.

#### **Overview**

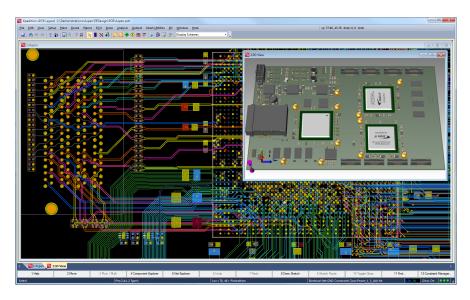

Xpedition<sup>®</sup> PCB layout is an essential part of the tightly integrated Xpedition Enterprise product family. By combining ease-of-use with designer-assisted advanced functionality, it offers designers and engineers industry-leading technology to create today's most complex designs. The layout environment includes automated placement planning and management, auto-assisted routing, customizable multi-pass autorouting, and more. It effectively handles the design challenges of large numbers of constraints, complex placement and net tuning, high performance differential pair routing, and HDI / micro-via technology, while optimizing for manufacturing design quality.

Xpedition's layout solution is a common, integrated environment that eliminates the data loss when jumping between tools to complete your job. The power of an industry-leading design environment enabling full placement and route planning and designer assisted routing technology. Designers and engineers can collaborate and easily manage electrical and manufacturing rules from a common database within a single environment for design, placement, and routing.

The integrated constraint management allows designers and engineers to enter comprehensive physical and electrical rule definitions that ensure the design quality via online and batch rule verification. This correct by construction methodology allows designs to be completed faster and with fewer manufacturing iterations by obeying the constraints throughout the design cycle.

The Xpedition layout tool also has industry-leading advanced technology, including: integrated 3D layout, rigid-flex layout, RF, and embedded design with cavity and wire bonding, and the award winning, collaborative, multi-user

A T A S H E E T

#### **MAJOR BENEFITS:**

- The integrated, planning, place and route editing environment reduces total design time and increases productivity

- Addresses your greatest PCB design challenges, including differential pair routing, net tuning, manufacturing optimization and BGA fanouts with micro-via technology

- Personalized user interfaces, object-action structure, and a common rules database drive productivity

- Advanced auto-assist planning, placement and routing, includes dynamic plane healing and teardrop creation, to decrease cycle times of complex, dense designs

- The correct-by-construction design methodology produces high-quality results and eliminates cleanup time

- Concurrent, single database, multiuser design layout environment enables efficient team resource management and dramatically shortened design time

- Fully integrated, true parametric, 3D layout with placement, constraints, DRC checking, and photo realistic visualization minimizes MCAD iterations

- Advanced Packaging and Rigid-Flex technologies allow easy creation of complex designs using the latest technology

system powered by Xtreme technology. The advanced design capabilities can tackle any of the requirements within today's PCB design technology.

From the simplest of drawing tasks, to the complex processes of defining high-speed constraints, to the placement and routing of dense, manufacturable designs, the correct-by-construction methodology provides a net result of reduced design cycle times, increased productivity and unmatched design quality.

#### Layout Technology

- A single integrated place, route and editing environment reduces design cycle time and increases productivity

- Common schematic and layout database for physical and electrical constraint management throughout the design cycle

- Automated placement planning and management for more efficient floor planning

- Correct-by-construction design produces high-quality results and eliminates clean-up time

- Advanced auto-assisted interactive shape-based planning and routing including any angle and curved trace routing

- Customizable multi-pass constraint driven autorouting with correct-by-construction results

- Dynamic DFM validation and cleanup of designs for improved manufacturing yields

#### **Constraint-Driven Design**

#### **Constraint Definition**

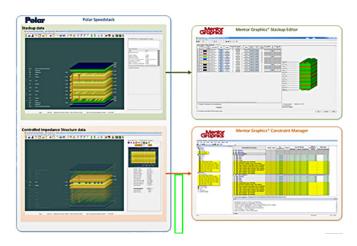

You can manage an extensive set of constraints to meet high-speed and DFM performance requirements, whether you're routing interactively or automatically. A single constraint management environment is shared between schematic capture and layout, and you may use the context-sensitive constraint editor, embedded directly within the schematic and layout environments, to define constraints at any design stage. Constraints include same layer and adjacent layer differential pairs, controlled impedance, net scheduling, match groups, complex and custom topologies, pin-pairs and pin-set rules, min/max/ match length and delay, Z-axis clearances, and much more. You can also manage package to package constraints for 2D or 3D layout that will optimize placement clearances for assembly manufacturing requirements.

Build PCB Layer stackup information through import of common industry formats from fabrication vendors. Then reuse the information on similar designs as required. Impedance model information can also be imported to build constraints for the designs high speed requirements.

Import and Reuse layer stackup information from your fabrication vendors.

#### **Correct-by-Construction**

Designers are increasingly challenged to automatically manage a complex set of system constraints that cannot be manually managed, to achieve system performance and reduce prototype iterations. The correct-byconstruction methodology improves overall efficiency and quality by reducing time-consuming cleanup of rules violations and ensuring that the design is correct throughout the design process, so you can get it "Right the first time!" Dynamic validation of physical and electrical rules, and dynamic tuning keeps nets in tune to ensure that the layout is meeting the engineering design intent.

#### **Placement Planning and Management**

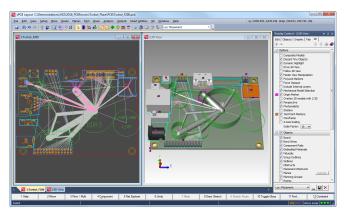

Placement planning allows a designer to quickly visualize and implement the engineer's design intent to quickly produce an optimal component placement. Component groups can be pre-defined in the schematic and are easily managed in the PCB as you develop a placement strategy using a personalized spreadsheet interface, and can also be per-defined in the schematic. This allows a top-down approach for planning of component groups producing an optimized connectivity definition before spending time implementing individual component locations. Once planned, groups can be quickly arranged based on the connectivity and refined. Placement planning and management with easy to use alignment and spacing tools will add speed and efficiency to the placement phase of your layout schedule.

*Hierarchical component grouping captures engineering intent and simplifies planning and placement.*

#### **Designer Assisted Auto Routing**

#### **Sketch Routing**

Auto assisted routing provides the speed and efficiency of auto routing, with complete user control and high quality. Starting with the Sketch Router, a designer can draw a sketch path to guide the location for the routing of the connections. The Sketch Router will route individual, dozens, or even hundreds of netlines many times faster than manual routing. Sketch routing focuses on quality; little cleanup is needed, often none at all. The high routing completion rate (typically >90%) is due to its ability to automatically optimize the escapes from components like BGAs so they are optimal for routing without any additional vias. The Hug Router can be applied for routing that does not complete to 100%. Hug Router extracts the design intent using existing routing to create a local bias to automate the routing process.

Sketch planning allows the designer to develop an optimized routing strategy using sketch plans. These plans can be manipulated like regular traces and contain the same functionality as the Sketch Router. Sketch plans can be routed in a batch mode routing multiple plans at one

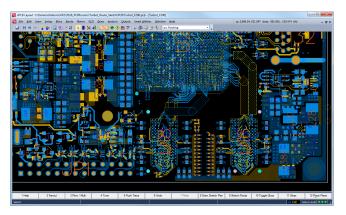

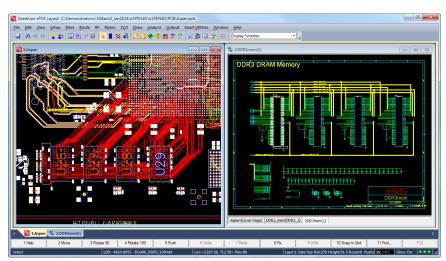

PCB layout is facilitated with powerful differential pair routing and net tuning capabilities for advanced high-speed designs.

time. Also included with Sketch Planning is the Trunk Router which allows the designer to plan and route sketch plans without optimizing the ends of the plan. This is useful when I/O optimization is still being done to your BGAs. Trunk Router also include full support of shielding and via stitching options during routing.

When interactively routing individual nets, Real Trace Plow minimizes the effort for single-ended and differential pair nets by flowing the traces behind the cursor — no more clicks are needed, not even to finish!

Real Trace Plow routing automation guides the routing with dynamic visual feedback while pushing and shoving vias and traces out of the way, and even clearing plane areas as you route. Additional controls allow the user to add design tolerances to aid in higher board fabrication yields. When there is a large set of routes that need to be moved, even across rule areas, the Dynamove capability enables smooth and fast movement of traces while it automatically removes extra segments and maintains high quality. Additionally, in non-symmetric pad arrays where 45 degree routing is prevented, you can easily route between pads at odd angles and around pads with curves to escape the most challenging BGA patterns.

#### **Net Tuning**

Multiple methods of tuning traces in your design are provided to decrease routing schedules. Automatic tuning provides the user with the power to open up dense areas of a board to add length to traces where needed. Nets can also be tuned within an autoroute pass. or automatically based on selection to meet length and electrical rules that may also include package lengths and via delay/ lengths. Additionally, automatic phase or sawtooth tuning of differential pairs is accomplished using your timing constraints. Once constraints are met, automatic tuning will keep nets tuned even during push and shove operations. While routing interactively, graphic tuning aids are displayed for guidance, and routes are automatically tuned as connections are completed. Advanced auto-assisted tuning allows the designer more interactive control to precisely add length to meet the most complex constraint definitions. The Dynamic Hazards function updates as you edit nets, providing instant feedback relative to your constraints.

#### **Differential Pair Routing**

Routing and editing differential pairs is accomplished with speed and ease that will change your view of highspeed design. Impedances can be easily controlled by layer- and pair-spacing rules. If one trace is edited, the other trace in the pair automatically moves with it. Routing differential pairs through staggered pins or dense areas is easily accomplished using curved and any

angle traces. Pad entry and via control are automated to provide for symmetric pad entry with short convergence. Broadside or adjacent layer differential pair routing capabilities add another valuable option for routing critical signals on a dense PCB.

#### **Advanced Interconnect Routing (HDI)**

Today's high density designs that include the highest pincount packages with very fine pitch pins/balls like BGA, CSP, COB, and DCA, require complex via structure rules and the routing of microvia geometries, including comprehensive via-in-pad rules. These designs move beyond the method of traditional laminate layer pairing.

PCB layout facilitates the design of build-up structures on laminate, and provides full user control of both stacked and staggered microvia structures and how they are defined, placed and edited. If needed, dynamic pad

removal of vias and through hole pads can be used to increase the routing space for dense designs, and the system will maintain proper DFM clearances between drilled holes or pads as needed.

PCB layout provides advanced tools for build-up and microvia structures with customized patterns.

effects on the plane metal to ensure design changes meet your electrical requirements. Complex area fill strategies can be created based on thermal or connectivity requirements, for example on high pin count devices. Area fills automatically heal around traces, vias, pads and other fills as the board is edited. Moving a via pushes and shoves other vias, traces, and area fills and connectivity is automatically maintained. Advanced z-axis constraints also dynamically clear area fills on adjacent layers, when required.

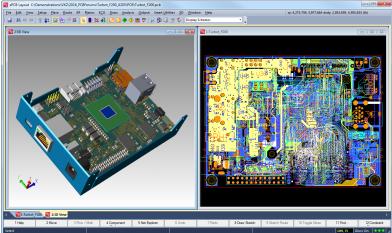

#### **3D Layout**

One of the challenges to integrating your PCB design process into the electromechanical world is the ability to left-shift validation into the PCB layout processes to find electromechanical design. 3D layout is a fully integrated 2D/3D environment and uses the same selection, planning

> and placement functionality as the PCB layout tool. The true parametric 3D mechanical kernel uses a complete set of 3D constraints with dynamic collision detection and batch verification to ensure your electromechanical designs are error free. Full photo-realistic visualization of board elements, like traces, components, silk screen, solder mask, and vias, is provided with transparency, z-axis scaling, view/rotation control, and x/y/z cut planes.

Included with 3D layout is ~4.9 million-part 3D model library. The ability to import your own models or even create your own models from parametric component templates is also available. 3D models can be easily managed within the context of the design, or as part of the overall enterprise library configuration. You can also import mechanical components like chassis and heat

#### **Rules by Area**

Advanced routing

automation allows rapid

and feel of hand routing.

routing of customized

Rules by Area allows a designer to take into account high areas of density limiting the impact to overall design manufacturability, yield and cost. Rule areas represent complete physical rule sets that are obeyed by online and batch design rule checking (DRC) and in interactive and automatic routing. Trace widths, via sizes and spans, and clearances dynamically change when traversing into or out of the rule area.

escape patterns from dense, high-pin-count devices.

automatically optimized spontaneously, all with the look

Complex breakouts from dense packages can be

#### **Dynamic Area Fill**

Dynamic Area Fill allows a designer to see the actual plane metal as it will be manufactured during the entire design process. This allows visualization of the placement and routing

3D visualization, placement and validation optimizes PCB electromechanical design.

sinks, and even sub-assemblies of other PCB designs, providing true mechanical multi-board capability.

Once your design is complete, you can use the integrated MCAD Collaboration tool to collaborate with popular industry mechanical design systems. You can also export your design in standard industry formats, and utilize the 3D PDF and documentation tools to complete your design package.

Xpedition 3D layout is a key element in your PCB design toolkit to be first to market with today's advanced electromechanical designs.

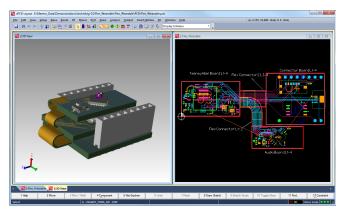

#### **Rigid-Flex Layout**

Many new electromechanical products are driving the need for flex and flex rigid systems. Along with the integrated 3D flow in Xpedition we have a best-in-class flex design flow. Flex and Rigid-flex PCBs addresses the challenges of highly complex and dense designs that must operate in rugged conditions. Flex systems are lightweight, compact, and durable, allowing the product to to be optimized within a very complex mechanical envelope by using all three dimensions.

Xpedition flex rigid design capabilities allow the designer to model the electrical product with multiple stackups by area including defined stiffener, cover layer and bend areas. User control over all of the parameters of a flex design are easily accomplished, and once completed, can be visualized and checked for mechanical clearances within the integrated 3D environment.

*Easily design and verify rigid-flex products within the Xpedition integrated 3D environment.*

#### **Design Reuse**

Design reuse automates the process of copying circuits to reduce the overall PCB design cycle time while improving quality by using known good IP. Integrated copy-circuit functionality allows circuits to be copied and pasted within and between designs with advanced equivalency algorithms to automatically map the schematic logic to the circuit during the copy process. In addition, the use of group planning and placement makes design reuse even more powerful. A formal design reuse module creates and stores reusable blocks of circuitry — including schematic and PCB placement and routing data — in a central library. This IP can be shared across the enterprise and can be placed and modified within the same design and across multiple designs.

#### **Variant Management**

The variant manager tool handles the creation of multiple

The embedded schematic view provides a current snapshot of the design for cross-probing and placement within PCB layout.

product configurations from a single design database. The integrated management interface minimizes errors, reduces costs, improves design quality and enhances production efficiency. The layout environment allows concurrent variant definitions within the schematic and layout, as well as function-managed variants. Once defined, variant documentation drawing output and bill of materials can automatically be created.

### **Design Collaboration** Schematic Design Collaboration

Engineering design changes can cause delays and introduce errors. Design collaboration eliminates the barriers of restricting changes within a schematic/

layout flow. Whether a single schematic designer, or multiple schematic designers collaborating, Xpedition supports concurrent constraint and logic changes while the layout is in progress, synchronizing the schematic and layout with powerful integration features. Changes made to the schematic and/or layout are easily updated into a common database without interrupting the design cycle. PCB designers also have access to an embedded schematic view within the layout tool.

#### **Concurrent Team Design**

Award winning Xpedition team layout, powered by Xtreme technology, allows multiple designers to work simultaneously within a single PCB layout design database. For PCB designs that have aggressive schedules, concurrent layout enables collaboration across geographically dispersed or functionally organized PCB design groups to maximize productivity and dramatically shorten design time to market. It is designed for immediate deployment, and is as fully functional as its single user counterpart. Time consuming training is not needed, or changes to a company's infrastructure or library to implement. Refer to the Xpedition xPCB Team Layout data sheet for complete details.

#### **Design Validation**

#### **Hazard Review**

During layout, constraint requirements can change. Designers must be able to validate the layout at any point to the constraint definition. Complete online electrical, and batch design rule validation make it easy to verify that your design is correct-by-construction. Design hazards are dynamically displayed and cross-probed in the design. An easy to use personalized spreadsheet allows the designer to review online, batch and 3D design hazards dynamically and then cross-probe to them in the design.

Hazards can be colored for easy identification. Once identified, clearance violations can be individually- or multi-

selected for automatic repair. When a hazard is fixed, it is dynamically removed from the hazard list. The tabulated spreadsheet also allows the designer to review hazards checked within other tools like Hyperlynx DRC and Valor NPI inside the Xpedition flow, all in one single and easy to read location.

#### **Design for Manufacturing (DFM)**

Creating and distributing manufacturing data to production sites introduces challenges at a point in the design process where errors can become very costly, both in time and money. The constraint manager contains manufacturing rules that optimize component clearances and physical clearances by area, and are dynamically checked during the design process. Advanced autoassisted interactive routing optimizes routing features on-the-fly checking to reduce manufacturing issues. In addition, there is tight integration with Mentor Graphics Valor NPI, allowing layout designers to leverage the same constraints used for final verification at manufacturing vendors, and check any hazards created using the dynamic design validation environment with a left-shift method of accessing the industry-premier solution for DFM validation.

Manufacturing documentation and outputs can be directly created within the layout environment, so any last minute layout changes are automatically synchronized. Automated and customizable creation and distribution of manufacturing data results in increased quality, accuracy

|  | <b>S</b> 🔶 «               | Valor-NPI Measurement Description | Test Value (th) | Layers                                 | Measurement Location (th) | Feature Description                |

|--|----------------------------|-----------------------------------|-----------------|----------------------------------------|---------------------------|------------------------------------|

|  | Valor-NPI (3227)           | Close Holes Same Net              | 15              | Drill Span 1 - 12                      | 1.180, 483                | pad(r8),pad(r8)                    |

|  | - 📕 🔽 Valor-NPI Red (15)   | Close Holes Same Net              | 15              | Drill Span 1 - 12                      | 302.172, 572.828          | pad(r8),pad(r8)                    |

|  | Valor-NPI Yellow (55)      | Close Holes Same Net              | 15              | Drill Span 1 - 12                      | 1.092.172, 1.527.172      | pad(r8),pad(r8)                    |

|  | 🔳 🔽 Valor-NPI Green (3157) | Close Holes Same Net              | 15              | Drill Span 1 - 12<br>Drill Span 1 - 12 | 1,092.172, 1,502.828      | pad(r8),pad(r8)                    |

|  | Valor-NPI Blue (0)         | Close Holes Same Net              | 15              | Drill Span 1 - 12<br>Drill Span 1 - 12 | 287.172, 587.828          | pad(r8),pad(r8)                    |

|  |                            | Close Holes Same Net              | 15              | Drill Span 1 - 12                      | 218.5, 620                | pad(r8),pad(r8)                    |

|  |                            | Close Holes Same Net              | 15              | Drill Span 1 - 12<br>Drill Span 1 - 12 | 930, 1,734                | pad(r8),pad(r8)                    |

|  |                            | Close Holes Same Net              | 15              | Drill Span 1 - 12<br>Drill Span 1 - 12 | 1,194, 1,745              | pad(r8),pad(r8)                    |

|  |                            | Close Holes Same Net              | 15              | Drill Span 1 - 12<br>Drill Span 1 - 12 | 1,194, 1,745              | pad(r8),pad(r8)                    |

|  |                            | Close Holes Same Net              | 15              | Drill Span 1 - 12<br>Drill Span 1 - 12 | 1,099, 1,745              | pad(r8),pad(r8)<br>pad(r8),pad(r8) |

|  |                            | Close Holes Same Net              | 15              | Drill Span 1 - 12<br>Drill Span 1 - 12 | 323.5, 520                |                                    |

|  |                            | Close Holes Same Net              | 15              | Drill Span 1 - 12<br>Drill Span 1 - 12 | 346, 520                  | pad(r8),pad(r8)                    |

|  |                            | SMD Pitch                         |                 | signal 1                               |                           | pad(r8),pad(r8)                    |

|  |                            |                                   | 20              |                                        | 3,356.618, 1,115.961      |                                    |

|  |                            | SMD Pitch<br>SMD Pitch            | 20              | signal_1                               | 934.039, 289.495          |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 254.998, 2,354.134        |                                    |

|  |                            |                                   | 20              | signal_1                               | 206.77, 2,362.008         |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 1,064.539, 289.495        |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 1,064.539, 348.55         |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 1,195.039, 289.495        |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 1,195.039, 348.55         |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 1,425.545, 2,198.569      |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 1,484.6, 2,214.317        |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 934.039, 348.55           |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 1,485.039, 289.495        |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 1,485.039, 348.55         |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 1,600.039, 289.495        |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 1,600.039, 348.55         |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 1,715.039, 289.495        |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 1,715.039, 348.55         |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 2,803.858, 2,221.895      |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 2,862.913, 2,237.643      |                                    |

|  |                            | SMD Pitch                         | 20              | signal_1                               | 3,297.562, 1,100.213      |                                    |

|  |                            | SMD Pitch                         | 20              | signal 1                               | 770 12 958 5              |                                    |

An easy to use integrated spreadsheet aids in the review of all hazards within the design, including those from other tools like Valor NPI.

and design throughput. Data can be output to manufacturing using the ODB++ format, ensuring that all manufacturing data is included and synchronized, and the design intent is maintained. Additional CAM formats and reporting, including Gerber, NC drill, and pick and place, are also supported.

#### **Advanced and Emerging PCB Technologies**

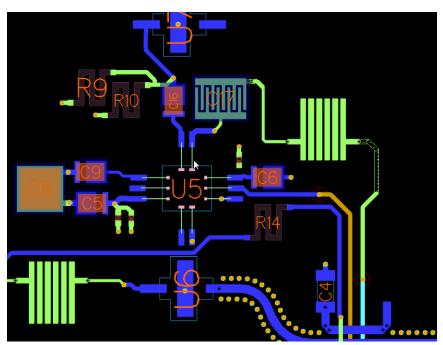

#### **RF Circuit Design**

RF circuits can be designed directly into your PCB layout or you can transfer designs from Agilent and AWR tools using the dynamic link, eliminating error prone translation processes. PCB layout understands the RF circuitry, and is not simply translating the design. Schematic entry and RF be implemented as embedded based on board size and cost, passive material choices, automatic synthesis driven by material supplier's libraries, and full manufacturing data generation. Embedded active components can also be utilized in your most advanced designs.

#### **Automation**

With the RF design tool, RF shapes are defined and placed from the schematic, and meanders can be added at any time.

circuit layout can be started in one environment and continued in the other; the dynamic link gives maximum flexibility. The simulation, tuning, and optimization capabilities of the RF simulation environment are supplied by the RF simulator. The dynamic link transfers the complete RF circuit intent to the RF simulator. This is done by transferring only what the RF simulator needs for a successful simulation, not the entire circuit.

#### **Embedded Passive/Active Design**

Xpedition automates layout creation with embedded passive/actives that used to take weeks of manual effort. As ICs and FPGAs increase in speed and density, they require more passive components (resistors and capacitors) — some may need several hundred. Implementing these as embedded components versus discrete SMDs can significantly reduce board sizes and improve performance. A complete embedded solution is provided: trade-off tools decide which components can Automation provides customization capability to automate specific and unique design processes for greater efficiency. Extensibility within the design and layout products, allows creation of custom functionality, automation of repetitive tasks, and the ability to tailor the flow to customerspecific use cases. The use of a wide range of industry standard languages (VBscript, Jscript, TCL, Java, VB6, C++, C#, VB.NET...) minimizes start-uptime for company programmers and facilitates script reuse. As a result, automation reduce errors, increases productivity, increases the performance, quality, and reliability of the design, decreases the cost of the design, and decreases time to market (and time to profit).

#### **Advanced Packaging**

Typically, die level packaging design is done in a separate tool, but with Xpedition, embedding die level packaging into your layout using wire

bonding technology is available within the same integrated database. Advanced constraint definitions for cavity design, chip-on-board, and multi- and stacked-dies are maintained in the integrated constraint manager. Easeof-use wizards are provided to create advanced die bond patterns, and wire bonds can be validated for DRC errors using 3D visualization.

3D visualization with DRC validation of wire bond and cavity designs improves the quality in advanced packaging applications.

#### **Customer Solutions**

There are a wide range of services are available to ease the transition to the Xpedition flow, including self-paced tutorials, design-ready, high-quality starter libraries, interfaces to popular front-end tools, design translators and translation services, and migration services. Whether a new or seasoned user, whatever your need, Mentor Graphics can help you get productive quickly and become an Xpedition expert.

Self-paced tutorials and on-demand video training get you up to speed and designing quickly!

#### For the latest product information, call us or visit: www.mentor.com/pcb

©2016 Mentor Graphics Corporation, all rights reserved. This document contains information that is proprietary to Mentor Graphics Corporation and may be duplicated in whole or in part by the original recipient for internal business purposes only, provided that this entire notice appears in all copies. In accepting this document, the recipient agrees to make every reasonable effort to prevent unauthorized use of this information. All trademarks mentioned in this document are the trademarks of their respective owners.

Corporate Headquarters Mentor Graphics Corporation 8005 SW Boeckman Road Wilsonville, OR 97070-7777 Phone: 503.685.7000 Fax: 503.685.1204

Sales and Product Information Phone: 800.547.3000 sales\_info@mentor.com Silicon Valley Mentor Graphics Corporation 46871 Bayside Parkway Fremont, CA 94538 USA Phone: 510.354.7400 Fax: 510.354.7467

North American Support Center Phone: 800.547.4303 Europe Mentor Graphics Deutschland GmbH Arnulfstrasse 201 80634 Munich Germany Phone: +49.89.57096.0 Fax: +49.89.57096.400

Pacific Rim Mentor Graphics (Taiwan) 11F, No. 120, Section 2, Gongdao 5th Road HsinChu City 300, Taiwan, ROC Phone: 886.3.513.1000 Fax: 886.3.573.4734 Japan Mentor Graphics Japan Co., Ltd. Gotenyama Trust Tower 7-35, Kita-Shinagawa 4-chome Shinagawa-Ku, Tokyo 140-0001 Japan Phone: +81.3.5488.3033 Fax: +81.3.5488.3004

MF 08-16 1031452-w